Enhancement And Depletion Mosfet

- Basic Electronics Tutorial

- Electronic Components

The symbols for enhancement and depletion MOSFETs show a difference in the second vertical line from the left, marked in red. For the enhancement MOSFET this line is discontinuous. This shows that the MOSFET is switched off with a V GS = 0 V. With a V GS = 0 V a depletion MOSFET can conduct current, and this is shown by the dashed line. Main Difference Between Depletion MOSFET and Enhancement MOSFETMOSFETMOSFET is an acronym for Metal Oxide Semiconductor Field Effect Transistor. It is a type of FET (Field Effect Transistor) that has an insulated metal oxide layer between its gate and channel. On the contrary, JFETs gate is connected with its channel. When first learning about MOSFETs, I got NMOS vs PMOS and enhancement vs depletion mode MOSFETs confused. So we decided to compare NMOS and PMOS MOSFETs.

- Resistors

- Capacitors

- Inductors

- Transformers

- Diodes

- Transistors

- Basic Electronics Useful Resources

- Selected Reading

The JFET is abbreviated as Junction Field Effect Transistor. JFET is just like a normal FET. The types of JFET are n-channel FET and P-channel FET. A p-type material is added to the n-type substrate in n-channel FET, whereas an n-type material is added to the ptype substrate in p-channel FET. Hence it is enough to discuss one type of FET to understand both.

N-Channel FET

The N-channel FET is the mostly used Field Effect Transistor. For the fabrication of Nchannel FET, a narrow bar of N-type semiconductor is taken on which P-type material is formed by diffusion on the opposite sides. These two sides are joined to draw a single connection for gate terminal. This can be understood from the following figure.

These two gate depositions (p-type materials) form two PN diodes. The area between gates is called as a channel. The majority carriers pass through this channel. Hence the cross sectional form of the FET is understood as the following figure.

Ohmic contacts are made at the two ends of the n-type semiconductor bar, which form the source and the drain. The source and the drain terminals may be interchanged.

Operation of N-channel FET

Before going into the operation of the FET one should understand how the depletion layers are formed. For this, let us suppose that the voltage at gate terminal say VGG is reverse biased while the voltage at drain terminal say VDD is not applied. Let this be the case 1.

In case 1, When VGG is reverse biased and VDD is not applied, the depletion regions between P and N layers tend to expand. This happens as the negative voltage applied, attracts the holes from the p-type layer towards the gate terminal.

In case 2, When VDD is applied (positive terminal to drain and negative terminal to source) and VGG is not applied, the electrons flow from source to drain which constitute the drain current ID.

Let us now consider the following figure, to understand what happens when both the supplies are given. Install sap gui for java on mac.

The supply at gate terminal makes the depletion layer grow and the voltage at drain terminal allows the drain current from source to drain terminal. Suppose the point at source terminal is B and the point at drain terminal is A, then the resistance of the channel will be such that the voltage drop at the terminal A is greater than the voltage drop at the terminal B. Which means,

VA>VB

Hence the voltage drop is being progressive through the length of the channel. So, the reverse biasing effect is stronger at drain terminal than at the source terminal. This is why the depletion layer tends to penetrate more into the channel at point A than at point B, when both VGG and VDD are applied. The following figure explains this.

Now that we have understood the behavior of FET, let us go through the real operation of FET.

Depletion Mode of Operation

As the width of depletion layer plays an important role in the operation of FET, the name depletion mode of operation implies. We have another mode called enhancement mode of operation, which will be discussed in the operation of MOSFETs. But JFETs have only depletion mode of operation.

Let us consider that there is no potential applied between gate and source terminals and a potential VDD is applied between drain and source. Now, a current ID flows from drain to source terminal, at its maximum as the channel width is more. Let the voltage applied between gate and source terminal VGG is reverse biased. This increases the depletion width, as discussed above. As the layers grow, the cross-section of the channel decreases and hence the drain current ID also decreases.

When this drain current is further increased, a stage occurs where both the depletion layers touch each other, and prevent the current ID flow. This is clearly shown in the following figure.

The voltage at which both these depletion layers literally “touch” is called as “Pinch off voltage”. It is indicated as VP. The drain current is literally nil at this point. Hence the drain current is a function of reverse bias voltage at gate.

Since gate voltage controls the drain current, FET is called as the voltage controlled device. Audio player for google slides. This is more clearly understood from the drain characteristics curve.

Drain Characteristics of JFET

Let us try to summarize the function of FET through which we can obtain the characteristic curve for drain of FET. The circuit of FET to obtain these characteristics is given below.

When the voltage between gate and source VGS is zero, or they are shorted, the current ID from source to drain is also nil as there is no VDS applied. As the voltage between drain and source VDS is increased, the current flow ID from source to drain increases. This increase in current is linear up to a certain point A, known as Knee Voltage.

The gate terminals will be under reverse biased condition and as ID increases, the depletion regions tend to constrict. This constriction is unequal in length making these regions come closer at drain and farther at drain, which leads to pinch off voltage. The pinch off voltage is defined as the minimum drain to source voltage where the drain current approaches a constant value (saturation value). The point at which this pinch off voltage occurs is called as Pinch off point, denoted as B.

As VDS is further increased, the channel resistance also increases in such a way that ID practically remains constant. The region BC is known as saturation region or amplifier region. All these along with the points A, B and C are plotted in the graph below.

The drain characteristics are plotted for drain current ID against drain source voltage VDS for different values of gate source voltage VGS. The overall drain characteristics for such various input voltages is as given under.

As the negative gate voltage controls the drain current, FET is called as a Voltage controlled device. The drain characteristics indicate the performance of a FET. The drain characteristics plotted above are used to obtain the values of Drain resistance, Transconductance and Amplification Factor.

Difference between enhancement and depletion type mosfet

Depletion mode MOSFET is normally turned on at zero gate voltage. Such devices are used as load resistors.

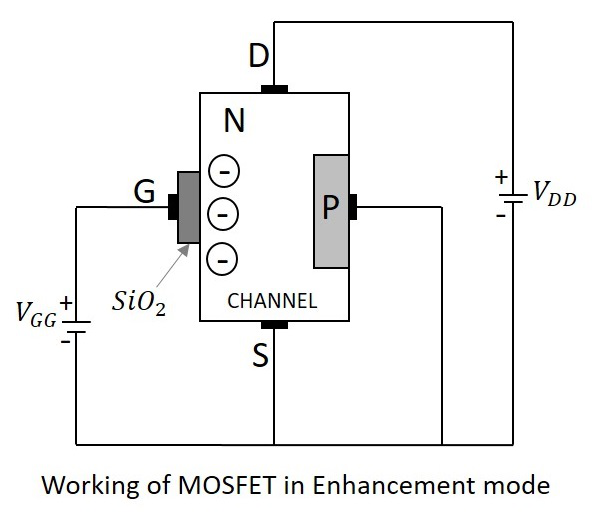

MOSFETs with enhancement modes are the common switching elements in most MOSs. These devices are deactivated at zero gate voltage and can be switched on by powering the gate.

In field effect transistors (FET), exhaust mode and amplification mode are two major types of transistor, corresponding to whether the transistor is in the ON or OFF state at zero gate-source voltage.

Enhancement MOSFET

MOSFETs with enhancement modes can be switched on by powering the gate either higher than the source voltage for NMOS or lower than the source voltage for the PMOS.

In most circuits, this means that pulling a MOSFET gate voltage into the leakage boost mode becomes ON.

For N-type discharging devices, the threshold voltage could be about -3 V, so it could be stopped by dragging the 3 V negative gate (leakage by comparison is more positive than the NMOS source).

In PMOS, polarities are reversed.

The mode can be determined by the voltage threshold sign (gate voltage versus source voltage at the point where only a layer inversion is formed in the channel):

- For a N-type FET, modulation devices have positive and depleted thresholds – modulated devices have negative thresholds;

- For a P-type FET, positive mode to improve negative mode, depletion.

Depletion MOSFET

Junction-effect junction transistors (JFET) are the depletion mode because the gate junction would transmit the bias if the gate was taken more than a bit from the source to the drain voltage.

Such devices are used in gallium-arsenide and germanium chips, where it is difficult to make an oxide isolator.

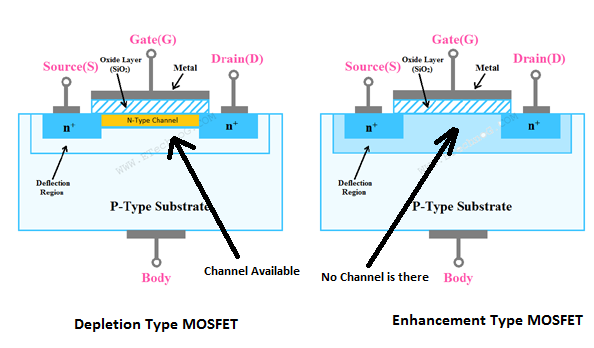

Figure describes the construction of MOSFET type of exhaustion. Also note the MOSFET circuit type N exhaust channel symbol.

Depletion Type Mosfet

Due to its construction, it offers very high entry strength (approximately 1010 to 1015). Significant current flows for VDS data at 0 volts VGS.

When the gate (ie, a capacitor plate) is made positive, the channel (i.e., the other capacitor plate) will have a positive charge induced therein.

This will lead to the depletion of the major bearers (ie electrons) and therefore to the reduction in conductivity.

Difference between enhancement and depletion type mosfet in tabular form

| Sr.No. | Depletion MOSFET (D-MOSFET) | Enhancement MOSFET (E-MOSFET) |

| 1 | It is called a depletion MOSFET because of channel depletion. | It only works in enhancement mode and is therefore called Enhancement MOSFET. |

| 2 | It can be used as E-MOSFET. | It can not be used as a D-MOSFET. |

| 3 | If Vgs = 0 V, Ids flows due to Vds. | If Vgs = 0V, Ids = 0, although Vds is applied. |

| 4 | N-type semiconductors exist in the structure itself between source and drain. | There is no n-channel between source and drain. |

| 5 | Do not occur | When Vgs = Vt, the MOSFET is turned on. |

Enhancement And Depletion Mosfet Chart

Now you know difference between enhancement and depletion mosfet.